# Radar Common Synchronization Protocol (RCSP)

Girish Kumar, Aarti Vimal, Rakesh Tripathi, Sheik Althaf M Electronics and Radar Development Establishment Defence Research and Development Organisation Bangalore, Karnataka, India-560093 girishkumar mrt@yahoo.com

#### Abstract:

Rotating Multi-Function digital phased array radars consist of synchronization unit to ensure that all sub-systems are synchronized using common reference. This unit performs synchronization of multiple sub-systems at data, signal, clock and RF levels. Based on level of required synchronization by subsystem, synchronization unit generate control messages, triggers and clocks. Different level demands multiple standard and specific physical interfaces & protocols to achieve sync in realtime. Traditionally serial and parallel interfaces are used for communicating data & signals and differential & analog interfaces for clocks & RF. We have developed radar common synchronization protocol (RCSP) based on high speed serial interface to send radar control message, signals and clock over single optical link for synchronizing multiple sub-systems. This protocol is tested in lab environment for synchronizing four subsystems with 10MHz clock, 10 timing signals and 10KB payload for synchronizing minimum of 1.2ms radar dwell.

Key Words: Synchronization, Multi-Function Radars, Timing Control Signals.

## I. INTRODUCTION

Multi-Function rotating phased array radar performs multiple functions such as searching, tracking, calibration, online Built In Testing (BIT), cued acquisition and ECCM. These functions need different radar times to achieve overall goal of radar operations. For ensuring that all subsystems of radar respond for different radar times, common synchronization unit is used to control data, signal and clock of radar sub-systems. Based on level of synchronization, this unit distributes control data, signals and clocks. Signal generation sub-system needs control data and multiple signals, Signal processing sub-system needs control data, Signal receiver sub-system needs control data and multiple signals, Radar encoder sub-system needs signals and clock.

Traditionally different physical interfaces were used to communicate with sub-systems using standard and customized protocols. Serial & parallel interfaces were commonly used for data and signals, differential & analog interfaces were used for clock and RF. Currently much advancements have happened in application of optical interface for communication. Multiplexing using coding technique is the current trend in sending multiple information over optical link. This technique is finding application in sending multiple RF over optical link. We have developed synchronization protocol specific to radar application for synchronizing radar subsystems based on high speed serial interface to send radar burst/dwell control message, multiple triggers and synchronized clock. This protocol is implemented in FPGA. Information required to be synchronized will be made available in message FIFO, number of signals and delay, duration and instances of signals will be written in specified register set by radar scheduler or radar burst controller. Clock will be generated from radar reference clock.

# **II.** ASSUMPTIONS

For this protocol to be applicable to current multi-function radars we have made certain assumptions. Assumptions are made to make sure that protocol finds application in multi function radars using available technologies. If assumptions are relaxed then performance and application of protocol will also get enhanced.

Here we have assumed that this protocol will be implemented on high speed serial optical link. Minimum packet shall be of 32 bits and not more than two 32 bit packets shall be used for packet overhead. FPGA device implementing protocol will be using clock better than 250MHz. Optical link must be supporting at least 250MBps.

This protocol will be point to point. In case of availability of copy mode for optical link, one level of cascading will be supported by this protocol.

Before this protocol is used for synchronization, physical link needs to be calibrated for packet delay which is dependent upon cable length and mode of operation. In future this calibration process can be made automatic.

Radar reference clock is available at synchronizing unit.

# **III. ARCHITECTURE**

RCSP is a point-to-point node based protocol. This protocol is hierarchy based having two levels of nodes; master and slave nodes. Protocol consists of one master named POST MASTER and has multiple slaves named POST MAN. **POST** stands for **P**rotocol generation, **S**ynchronization and **T**iming.

POST MASTER works in two modes: standalone mode and extended mode. In standalone mode, POST MASTER performs synchronization of sub-systems. SYNC Packets generated are used by POST MASTER to generate

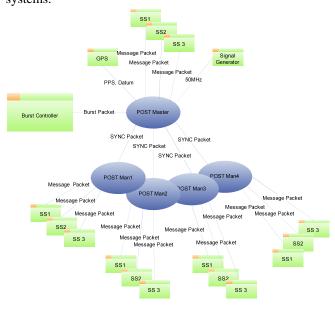

1. Figure : RCSP Architecture

POST MASTER interfaces with radar scheduler or burst controller sub-system for reception of burst packet. In standalone mode of operation, it is interfaced with other radar sub-systems for their synchronization. It generates control messages and timing signals for interfaced subsystems. In extended mode of operation, it is interfaced with a number of POST MAN using high speed serial interfaces for sending SYNC packets which in turn synchronize other sub-systems connected to POST MAN. SYNC packet contains timing control, triggers control and message data in protocol frame. POST MAN in turn prepares control message and generates timing signals for other interfaced sub-systems for their synchronization.

POST MASTER can drive three sub-systems and can synchronize four POST MAN for extension of synchronization control.

POST MASTER uses radar reference clock from signal generator for synchronization and GPS for time stamping purpose.

# 1. Burst Packet:

Burst packet contains complete information of next burst to be executed. This packet also includes time at which burst needs to be executed. Burst packet consists of characteristics of burst, information on number of subbursts, number of triggers during each sub-burst and delay & duration of each trigger.

# 2. Message Packet:

Message packet contains information for next burst to be played. Generally message packet is written in FIFO and followed by control word for starting relay of message to sub-system. Based on requirement of handshaking, acknowledgment is also processed to complete message sending. Checksum is added at the end of each message packet to ensure preparation, interpretation and transmission of correct message.

# 3. SYNC Packet:

SYNC packet contains information for next burst as well as the timing information for the current burst. Each data frame contains a start word, payload and an end word. Payload has current burst timing information as well as the control message for the next burst.

SYNC packet size is fixed for containing sub-burst information, number of triggers and part of message packet. SYNC packet also contains control word for staring of message packet. Number of SYNC packet is dependent upon size of burst but always padded with dummy packet to ensure timing is multiple of 10MHz. Packet contain timing offset field as well to precisely synchronize POST MASTER and POST MAN triggers.

# **IV. RCSP CONCEPT OF OPERATION**

This protocol packetizes the timing information in control words and control messages in a single optical data frame. The structure of data frame has start of frame, followed by control words and message and an end of frame. CRC can be used in data frame for error detection. The start of frame is the reference for the generation of timing signals. The control words contain the parameters such as authorization, delay and duration of timing signals to be generated with respect to the start of frame reference. The size of data frame depends on number of timing signals to be generated and maximum size of dwell messages for various interfaces.

For 10 MHz timing resolution, the size of frame should be selected to be multiple of 100ns. For 250 MBps link, the time taken for 32 bits is 16ns. So, if the frame size is taken to be of 800ns, then the number of 32 bit words in a frame will be 50. Out of 50 words, one word is used for start of frame and another for end of frame and remaining words is the payload which contains control words and control messages. So, the maximum efficiency will be (48/50)\*100 i.e 96%. The dwell of 1.2 ms will be divided into  $(1.2*10^{6})/800$  i.e 1500 data frames.

Information for next burst should reach fixed time before the start of next burst reference signal. For multiple sub-systems, let us assume that 600us time is required for the POST MASTER and POST MAN to meet the above delta time requirement. So, for dwell duration of 1.2 ms, 600us are left for sending control messages. But, since timing information is for the current burst, it is sent with each data frame.

Parameters such as authorization, duration and delay of timing signals are required for timing signals (triggers) generation. Each data frame consists of number of triggers and delay & duration of each trigger.

The 32-bit data words are first encoded and serialized at sender side. At receiver side, a de-serializer is used and then the data is decoded. For making the optical protocol self clocking, encoding is used such as 8b/10b.

The parameters are extracted from the payload for timing signals generation.

For phase alignment of timing signals, the extracted clock at receiver end should be phase corrected with the timing generation reference i.e the start of frame. Link delay for each interface will be benchmarked and configured as parameter to protocol for timing signals alignment. This needs process of calibration at regular interval to keep POST MASTER and POST man in synchronization.

## V. **RESULTS**

We have first implemented RCSP protocol in multi function radar using POST MAN configuration. After testing POST MAN, we extended protocol to POST MASTER configuration in lab environment. For timing based generation of SYNC message we have used CSAC based time reference system. In lab environment, protocol is tested for synchronizing four sub-systems. Some of the results are shown below:

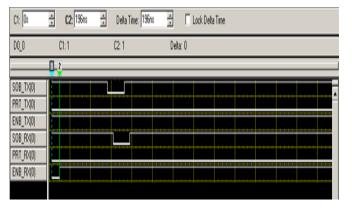

Following figures show the generation of synchronizing signals at POST MASTER and POST MAN using RCSP protocol. Figure1 shows reference synchronization signal for burst (Start of new burst, SOB) at POST MASTER and POST MAN.

| C1: 0\$   | ÷ C2: 4.1943ms | 🚊 Delta Time: 4 | 1943ms 🚊 🗌 Lock De | elta Time |   |

|-----------|----------------|-----------------|--------------------|-----------|---|

| D0_0      | C1: 1          | C2: 1           | Delta: O           |           |   |

|           | <u> </u>       |                 |                    | 2         | Ш |

| SOB_TX(0) |                |                 |                    |           | E |

| PRT_TX(0) |                |                 |                    |           | Ê |

| ENB_TX(0) |                |                 |                    |           |   |

| SOB_RX(0) |                |                 |                    |           |   |

| PRT_RX(0) |                |                 |                    |           |   |

| ENB_RX(0) |                |                 |                    |           |   |

|           |                |                 |                    |           |   |

2. Figure : Generation of synchronizing signals at POST MASTER and POST MAN.

Figure2 shows delay between the enable signal at POST MASTER and POST MAN.

3. Figure : Delay between the enable control at POST MASTER and POST MAN

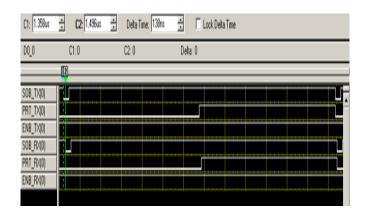

Figure3 shows the achieved synchronization level of triggers at POST MASTER and POST MAN.

4. Figure : Delay between the start of burst trigger at POST MASTER and POST MAN

# VI. CONCLUSIONS

This paper presents common synchronization protocol specific to radar application for synchronizing radar subsystems based on high speed serial interface which can operate over long distances. POST MAN mode is already tested in three multi function phased array radars. POST MASTER configuration of protocol is tested in lab environment for synchronizing four sub-systems: two subsystems local to POST MASTER and two sub-systems at POST MAN. We observed that discrete links required for transmission of timing signals for sub-systems synchronization reduced drastically. This protocol reduced spatial constraint of co-locating sub-systems of radar for enhancing operational effectiveness. This protocol is having inherent capability of accepting multi-aspect operations burst from other radars as well. This protocol needs calibration of delays over physical links between POST MASTER and POST MAN. Currently we have implemented method of manual calibrations but calibration process can be automated in future.

#### VII. REFERENCES

- [1] Merrill I Skolnik, "Introduction to Radar Systems," Tata McGraw-Hill, Third Edition, Aug 2000.

- [2] Jayaram Bhasker, "A VHDL Primer", P T R Prentice Hall, Third Edition, Sep 1998.

- [3] Douglas L Perry, "VHDL: Programming by Example", McGraw-Hill, Fourth Edition, May 2002.

- [4] Xilinx Virtex-5 Datasheet

# **BIO DATA OF AUTHOR(S)**

## Girish Kumar

Completed BTech in Electronics Engineering from UP Technical University, Lucknow, UP, India. He worked in ISRO for 2 years. He is currently working as a scientist in LRDE, DRDO, Bangalore. His main research interests are digital system design and development.

# Aarti Vimal

Graduated in Computer Science and Engineering from Motilal Nehru National Inst itute of Technology, Allahabad in 2003. She is working as a scientist in LRDE. Her main research interests are eneric software for radar systems, radar target classification and radar scheduling.

# Rakesh Tripathi

Received BE in CS&E from Kuvempu University, Davangere, Karnataka, India. M.Tech in Computer & IT from IIT Kharagpur, West Bengal, India. He is working as a scientist in LRDE, Bangalore lab. of DRDO. His main research interests are radar scheduling, multi staged target identification, radar time management, high performance computing and software design & engineering.

## Sheik Althaf M

Graduated in Electronics & Communication Engineering from Government college of engineering, Tirunelveli. Joined DRDO in year 1990. He is currently Scientist F'. His area of interests include radar system engineering, radar target simulation and generic software for radar systems.